74HC595N 8-bit shift register

Omschrijving

De 74HC595-datasheet specificeert dat dit IC een 8-traps seriële schuifregisters is met een opslagregister en 3-state uitgangen. De registers hebben aparte klokken. bevatten een 8-bit serieel-in, parallel-uit schuifregister dat een 8-bit D-type opslagregister voedt. Gegevens worden verschoven op de positieve overgangen van de schuifregisterklokingang (SHCP). De gegevens in elk register worden overgedragen naar het opslagregister bij een positieve overgang van de opslagregisterklokingang (STCP). Als beide klokken met elkaar zijn verbonden, zal het schuifregister altijd één klokpuls voorlopen op het opslagregister.

|

|

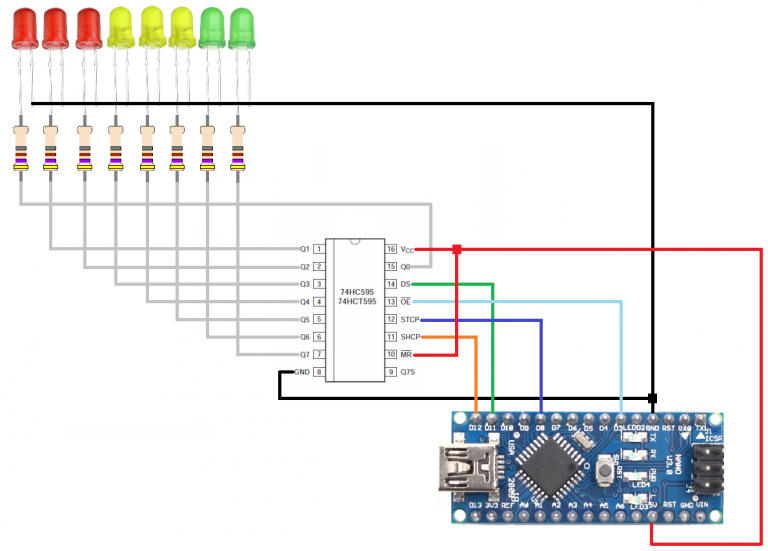

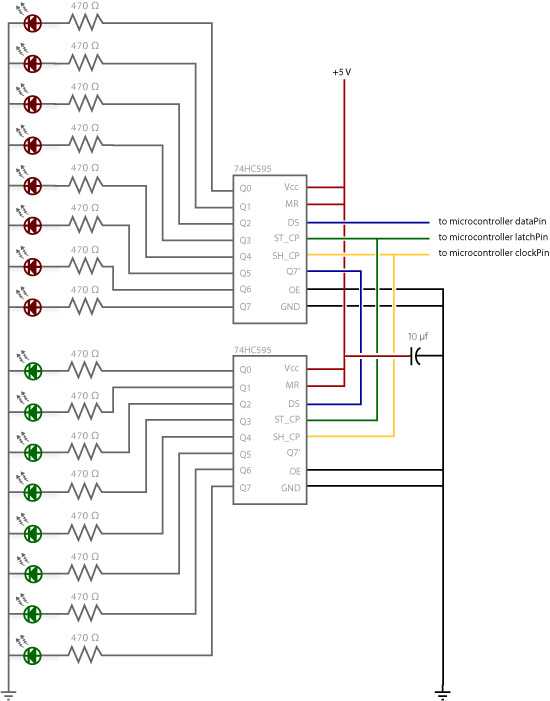

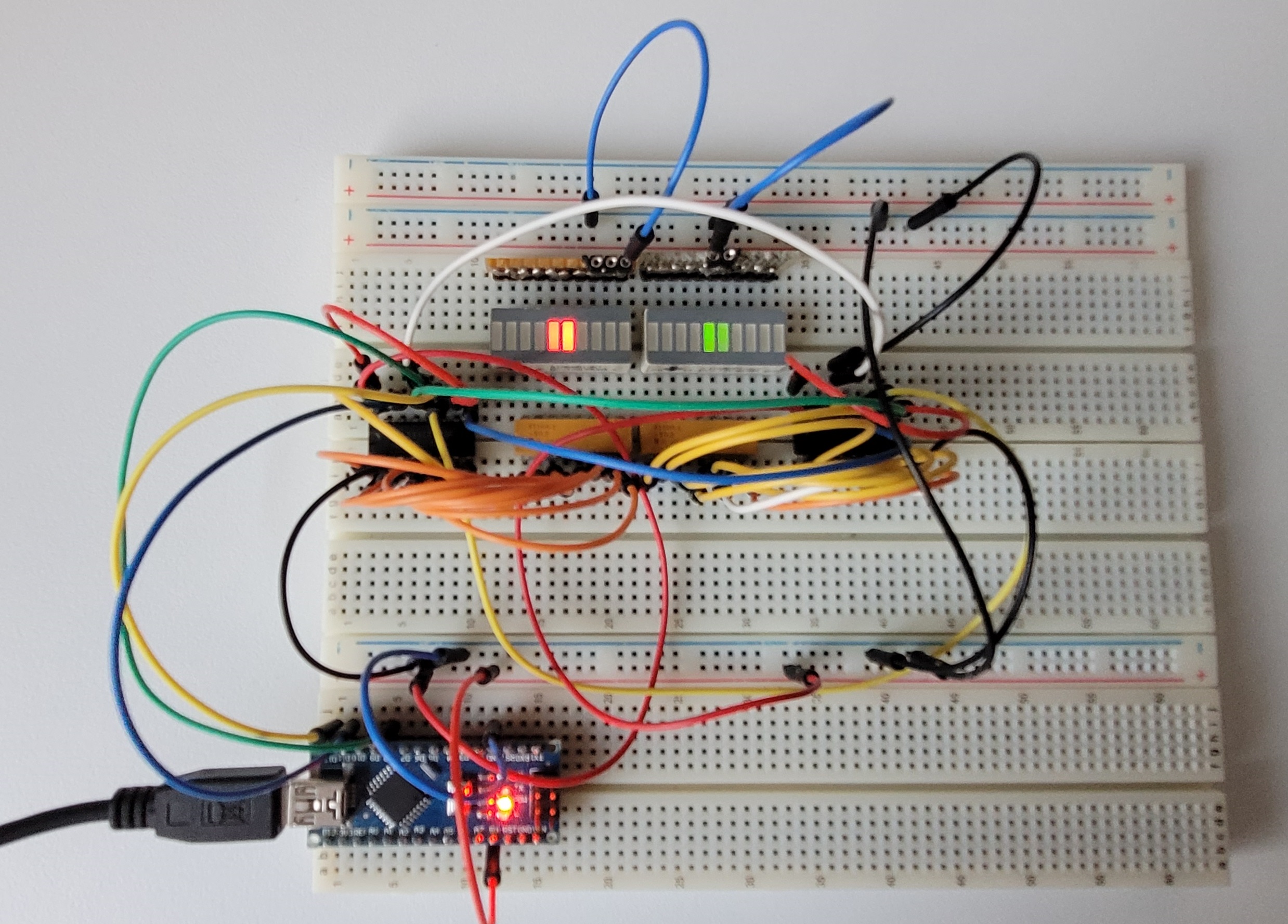

| Opstelling met 1 74HC595 | Opstelling met 2 74HC595 |

Hoe werkt het

Data komt serieel binnen, als alle bites binnen zijn, latch (bevries) je de chip, en op de 8 data lijnen staan de 8 bit’s (Byte) data.

Het is ook mogelijk om 2 of meerdere chip’s aan te sluiten. Er zit een overflow bit op (Q7S of Q7′), deze kan dan op de data van een volgende aangesloten worden. Op die manier kan je serieel 2 bytes (Word) maken.

Hieronder schematisch de werking voorgesteld.

Gemeten met de logic analyser:

Meer leesvoer: Serial to Parallel Shifting-Out with a 74HC595

Specificaties

- 8-bit serial input

- 8-bit serial or parallel output

- Storage register with 3-state outputs

- Shift register with direct clear

- 100 MHz (typical) shift out frequency

- CMOS low power dissipation

- voltage range from 2.0 to 6.0 V

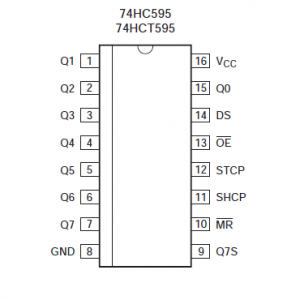

Aansluit schema / Pinouts

|

DS: Serieel in OE: Output enable STCP: RCLK SHCP: SRCLK MR: SRCLR Q7S: Overflow bit VCC: + 3,3 ~ 5 Volt GND: gnd Q0 t/m Q7: 8 bit out |

Uitleg pin’s

SRCLK (Shift Register Clock)

Is de clock voor het schuifregister. De 595 is ‘clock puls’ gestuurd op de als deze Hoog wordt. Dit betekent dat om bits in het schuifregister te schuiven, de clock HOOG moet zijn. En bits worden overgedragen op de stijgende clock puls.

RCLK (Register Clock / Latch)

Is een zeer belangrijke pin. Wanneer deze HOOG wordt, wordt de inhoud van Shift Register gekopieerd naar het Storage/Latch Register; die uiteindelijk sichtbaar wordt op de uitgang. Dus de latch kan worden gezien als de laatste stap in het proces om de data aan de uitgang te zien, in dit geval de LED’s.

SRCLR (Shift Register Clear)

Deze pin stelt ons in staat om het hele Shift Register te resetten, waardoor alle bits in één keer 0 (laag) worden. Dit is een negatieve logische pin, dus om deze reset uit te voeren; we moeten de SRCLR-pin LOW instellen. Als er geen reset nodig is, moet deze pin HOOG zijn.

OE (Output Enable)

Is ook negatieve logica: wanneer de spanning erop HOOG is, zijn de uitgangspinnen uitgeschakeld / ingesteld op een hoge impedantiestatus en laten ze geen stroom vloeien. Wanneer OE een lage spanning krijgt, werken de uitgangspinnen normaal.

Het is mogelijk om deze pin ook te gebruiken om de LED’s te laten dimmen, zie ook de downloads voorbeelden. (

Brightness_demo (270 downloads )

), dit kan door een PWM pin op de Arduino aan te sluiten op de OE pin van de chip.

Q0-Q7 (Output)

Zijn de output-pinnen en moeten worden aangesloten op een soort output zoals LED’s, 7 Segments enz.

Q7S / Q7′

Pin geeft bit 7 van het ShiftRegister weer. Deze pin kan je gebruiken om 595’s doorlussen: als je deze Q7S aansluit op de SER-pin van een andere 595, en beide IC’s hetzelfde kloksignaal geeft, zullen ze zich gedragen als een enkele IC met 16 uitgangen. Natuurlijk is deze techniek niet beperkt tot twee IC’s – je kunt er zoveel in serie schakelen als je wilt, als je genoeg stroom hebt voor allemaal.

Schema

Downloads

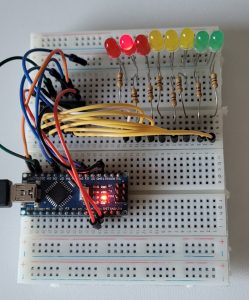

Demo met 1 74HC595

Nightrider_demo (318 downloads )

Brightness_demo (270 downloads )

Demo met 2 74HC595

dubbele_74HC595_2x_demo_1 (260 downloads )

dubbele_74HC595_2x_demo_2 (240 downloads )